Heft 10 · 1989

# Mikroprozessortechnik

VEB Verlag Technik Berlin

ISSN 0232-2892

## 1-Megabit-Speicher U 61000

CMOS-Mikroprozessorsystem

Hybridschaltkreise

**Herausgeber** Kammer der Technik, Fachverband Elektrotechnik

**Verlag** VEB Verlag Technik, Oranienburger Str. 13/14,

DDR-1020 Berlin; Telegrammadresse: Technikverlag

Berlin; Telefon: 28700, Telex: 011 2228 techn dd

**Verlagsdirektor** Klaus Hieronimus

**Redaktion** Hans Weiß, Verantwortlicher Redakteur (Tel. 2870371); Redakteure: Herbert Hemke (Tel. 2870203),

Hans-Joachim Hill (Tel. 2870209); Sekretariat Tel.

2870381

**Gestaltung** Christina Bauer

**Beirat** Dr. Ludwig Claßen, Dr. Heinz Florin, Prof. Dr. sc.

Rolf Giesecke, Joachim Hahne, Prof. Dr. sc. Dieter Hammer,

Prof. Dr. sc. Thomas Horn, Prof. Dr. Albert Jugel, Prof.

Dr. Bernd Junghans, Dr. Dietmar Keller, Prof. Dr. sc. Gernot

Meyer, Prof. Dr. sc. Bernd-Georg Münzer, Prof. Dr. sc. Peter

Neubert, Prof. Dr. sc. Rudolf Arthur Pose, Prof. Dr. sc. Dr.

Michael Roth (Vorsitzender), Dr. Gerhard Schulze, Prof. Dr.

sc. Manfred Seifart, Dr. Dieter Simon, Dr. Rolf Wätzig, Prof.

Dr. sc. Dr. Jürgen Zaremba

**Lizenz-Nr.** 1710 des Presseamtes beim Vorsitzenden des

Ministerates der Deutschen Demokratischen Republik

**Gesamtherstellung** Druckerei Märkische Volksstimme

Potsdam

**Erfüllungsort und Gerichtsstand** Berlin-Mitte. Der Verlag

behält sich alle Rechte an den von ihm veröffentlichten

Aufsätzen und Abbildungen, auch das der Übersetzung in

fremde Sprachen, vor. Auszüge, Referate und Besprechungen

sind nur mit voller Quellenangabe zulässig.

**Redaktionsschluß** 15. August 1989

**AN (EDV)** 49837

**Erscheinungsweise** monatlich 1 Heft

**Heftpreis** 5,- M, Abonnementspreis vierteljährlich 15,- M;

Auslandspreise sind den Zeitschriftenkatalogen des Außenhandelsbetriebes BUCHEXPORT zu entnehmen.

#### **Bezugsmöglichkeiten**

DDR: sämtliche Postämter; SVR Albanien: Direktorije

Quendrore e Perhapjes dhe Propagandit te Librit Rruja

Konferencës Pezes, Tirana; VR Bulgarien: Direkzia R.E.P.,

11a, Rue Paris, Sofia; VR China: China National Publications

Import and Export Corporation, West Europe Department,

P.O. Box 88, Beijing; ČSSR: PNS – Ustřední Expedicí

a Dovoz Tísku Praha, Slezská 11, 120 00 Praha 2, PNS,

Ústředna Expedicí a Dovoz Tlaco, Pošta 022, 885 47 Bratislava;

SFR Jugoslawien: Jugoslovenska Knjiga, Terazija

27, Beograd; Izdavačko Knjižarsko Producēce MLADOST,

Ilica 30, Zagreb; Koreanische DVR: CHULPANMUL Korea

Publications Export & Import Corporation, Pyongyang; Republik Kuba: Empresa de Comercio Exterior de Publicaciones,

O'Reilly No. 407, Ciudad Habana; VR Polen: C.K.P.i.W.

Ruch, Towarowa 28, 00-958 Warszawa; SR Rumänien:

D.E.P. Bucureşti, Piața Scînteii, Bucureşti; UdSSR: Sämtliche

Abteilungen von Sojuzpečat' oder Postämter und Postkontore; Ungarische VR: P.K.H.I., Külöföldi Előfizetési Osztály,

P.O. Box 16, 1426 Budapest; SR Vietnam: XUNHABABA,

32, Hai Ba Trung, Hanoi; BRD und Berlin (West):

ESKABE Kommissions-Grossbuchhandlung, Postfach

36, 8222 Ruhpolding/Obb.; Helios-Literatur-Vertriebs-

GmbH, Eichborndamm 141-167, Berlin (West) 52; Kunst

und Wissen Erich Bieber OHG, Postfach 46, 7000 Stuttgart 1; Gebrüder Petermann, BUCH + ZEITUNG INTERNATIONAL,

Kurfürstenstraße 111, Berlin (West) 30; Österreich: Helios-Literatur-Vertriebs-GmbH & Co. KG, Industrie-

straße B 13, 2345 Brunn am Gebirge; Schweiz: Verlagsauslieferung Wissenschaft der Freihofer AG, Weinbergstr. 109,

8033 Zürich; Alle anderen Länder: örtlicher Fachbuchhandel; BUCHEXPORT Volkseigener Außenhandelsbetrieb

der Deutschen Demokratischen Republik, Postfach 160,

DDR-7010 Leipzig und Leipzig Book Service, Talstraße 29,

DDR-7010 Leipzig

**40 Jahre DDR** – das bedeutet kontinuierliche Entwicklung unseres Staates und seit langem die Einheit von Wirtschafts- und Sozialpolitik. Folgerichtig war 1976 der Entschluß zur Entwicklung und breiten Anwendung der Mikroelektronik gefaßt worden, und die in unserer Zeitschrift bisher veröffentlichten Beiträge sind ein Ausdruck für die erfolgreiche Verwirklichung dieser Vorhaben. In unserem Mai-Heft konnten wir Sie beispielsweise umfassend über das neue, schnelle 16-Bit-Mikroprozessorsystem U 80600 aus dem VEB Kombinat Mikroelektronik Erfurt informieren, dessen Serienfertigung zu Ehren des 40. Jahrestages gegenwärtig beginnt.

In den beiden ersten Beiträgen dieses Heftes (**Seite 291** bzw. **Seite 292**) erläutern wir die Bedeutung der Megabitspeicher und stellen den 1-MBit-DRAM U 61000 ausführlich vor. Mit der Entwicklung dieses Speicherschaltkreises haben die Werktagen des VEB Carl Zeiss JENA Leistungen vollbracht, zu denen gegenwärtig nur wenige führende Länder bzw. Hersteller in der Welt in der Lage sind. Bekanntlich waren bereits im vergangenen Jahr erste Muster präsentiert worden, und zum diesjährigen Geburtstag der Republik kann die Aufnahme der Pilotproduktion abgerechnet werden.

Neben dem 16-Bit-Mikroprozessorsystem U 80600 zeigte das Kombinat Mikroelektronik zur Leipziger Frühjahrsmesse als weitere Neuheit sein erstes 8-Bit-System in der stromsparenden CMOS-Technik. Wir stellen Ihnen das System U 84C00 in diesem Heft ab **Seite 296** näher vor.

Ebenfalls zur diesjährigen Frühjahrsmesse offerierte das Kombinat Keramische Werke Hermsdorf in Leipzig Muster von 4-Megabitspeichern auf Hybridschaltkreisträgern. Sie bestehen, je nach Variante, aus jeweils 16 Chips des 256-KBit-DRAMs U 61256 oder 4 Chips des U 61000 aus dem Kombinat Carl Zeiss JENA. In dem Beitrag auf **Seite 298** wird ein Überblick über den Stand der Fertigung von Hybridschaltkreisen im Kombinat Keramische Werke Hermsdorf gegeben, der diese Speicherschaltkreise einschließt.

#### **Vorschau**

Für Heft 11 bereiten wir für Sie Beiträge zu folgenden Themen vor:

- Von Turbo 3.0 zu Turbo 5.0

- Multiprozessorsysteme mit U 8000

- Druckerinitialisierung

- DOS-Gerätetreiber für SCOM-LAN

## **Inhalt**

|                                                                                                                 |             |

|-----------------------------------------------------------------------------------------------------------------|-------------|

| <b>MP-Bericht</b>                                                                                               | <b>2.US</b> |

| 13. Mikroelektronik-<br>Bauelementesymposium                                                                    |             |

| <b>MP-Info</b>                                                                                                  | <b>290</b>  |

| <i>Bernd Junghans:<br/>Der Megabitspeicher<br/>und die Mikroprozessortechnik</i>                                | <b>291</b>  |

| <i>Jens Knobloch, Andreas Scade:<br/>Der Megabitspeicher U 61000</i>                                            | <b>292</b>  |

| <i>Michael Ritter:<br/>8-Bit-CMOS-Mikroprozessorsystem<br/>U 84C00</i>                                          | <b>296</b>  |

| <i>Bernd Racurow:<br/>Hybridschaltkreise aus Hermsdorf</i>                                                      | <b>298</b>  |

| <i>Johannes Rolf Hillig:<br/>Kontamination oder<br/>Reicht das Staubwischen<br/>in der Halbleiterfertigung?</i> | <b>299</b>  |

| <i>Jürgen Lampe:<br/>Erfahrungen mit Modula-2-Compilern</i>                                                     | <b>301</b>  |

| <b>MP-Kurs:</b><br>Manfred Zander:<br>Turbo-Pascal-Praxis (Teil 3)                                              | <b>303</b>  |

| <i>Andreas Holländer:<br/>Redabas-Tip<br/>Command Master</i>                                                    | <b>307</b>  |

| <i>Hans Dolleschel:<br/>Der Apple Macintosh</i>                                                                 | <b>308</b>  |

| <i>Heiko Wand:<br/>Arithmetik für die Meßtechnik</i>                                                            | <b>312</b>  |

| <i>Wegbereiter der Informatik:<br/>Ludwig Eduard Boltzmann</i>                                                  | <b>313</b>  |

| <b>MP-Computer-Club</b><br>Thomas Bauer:<br>Bildschirmsteuerung des PC 1715                                     | <b>314</b>  |

| <i>Michael Lennartz:<br/>Umcodieren der Steuertasten<br/>unter MS-DOS</i>                                       |             |

| <i>Helmut Schenk:<br/>Komfortable formatierte Eingabe<br/>in Basic</i>                                          |             |

| <b>MP-Börse</b>                                                                                                 | <b>316</b>  |

| <b>Entwicklung und Tendenzen</b>                                                                                | <b>318</b>  |

| <b>MP-Literatur</b>                                                                                             | <b>320</b>  |

# Der Megabitsspeicher und die Mikroprozessortechnik

**Prof. Dr. Bernd Junghans,

VEB Forschungszentrum Mikroelektronik Dresden

Betrieb des Kombinates VEB Carl Zeiss JENA**

Weshalb richtet sich in so ungewöhnlichem Maße die Aufmerksamkeit der Öffentlichkeit auf die Entwicklung von Halbleiterspeichern? Sind sie doch nur einer von Hunderten Bausteinen, die die Hardwarebasis der modernen Rechentechnik ausmachen. Gewiß sind sie ökonomisch wichtig, da sie bereits über einen langen Zeitraum und auch in der absehbaren Zukunft wertmäßig etwa 20 Prozent der Weltproduktion an integrierten Schaltkreisen ausmachen. Den Anwender dürfen aber mehr die Gebrauchswerte interessieren. Und tatsächlich ist ein Großteil des in den letzten Jahren erzielten atemberaubenden Fortschritts der Mikroprozessortechnik durch den Einsatz immer höher integrierter Speicherbausteine ermöglicht worden. Hatten noch vor rund 10 Jahren lediglich Großrechner eine Hauptspeicherkapazität von einigen Megabyte, so ist diese Größe heute bereits Standard bei Arbeitsplatzcomputern. Das war nur möglich durch die Steigerung des Integrationsgrades der Speicherschaltkreise in diesem Zeitraum um etwa drei Größenordnungen.

So wurde Anfang der 80er Jahre der Hauptspeicher für die EDVA EC 1055 mit einer Kapazität von 1 Megabyte durch 9 000 Stück 1-KBit-DRAM U 253 realisiert, wozu ein separater Schrank mit den Abmessungen von rund 0,7 m × 1,2 m × 1,8 m benötigt wurde. Es wäre weder ökonomisch erschwinglich, noch technisch sinnvoll, einem Personalcomputer einen solchen Schrank beizustellen. Die gleiche Speicherkapazität kann heute mit 9 Stück DRAM-Schaltkreisen U 61000 auf einer Leiterplattenfläche von rund 10 cm<sup>2</sup> untergebracht werden! Den durch die gewachsene Speichergröße möglich gewordenen enormen Gewinn an Rechnerleistung und Komfort wissen die Leser der „Mikroprozessortechnik“ selbst einzuschätzen.

Weniger bekannt dagegen ist häufig sogar unter Informatikern die fundamentale Bedeutung der Speicherschaltkreise als Schrittmacher für die Technologieentwicklung, die aber letztlich allein die Sonderstellung der Speicher unter allen mikroelektronischen Entwicklungen ausmachen. Seit dem Eintritt in das Zeitalter der Großintegration (LSI) Ende der 60er Jahre haben die Speicher mit einer Verdopplung des Integrationsgrades aller 1,5 Jahre das Tempo des technologischen Fortschritts in der Mikroelektronik bestimmt. Dabei erstreckt sich das für die Speicherherstellung erarbeitete umfangreiche Know-how nicht nur auf die Halbleitertechnologie an sich, sondern reicht von den einzusetzenden äußerst vielfältigen Chemikalien über die hochgezüchteten technologischen und meßtechnischen Ausrüstungen bis zur extremen Anforderungen genügenden Reinraumtechnik und rechnergestützten Produktionssteuerung.

So war zum Beispiel für die CMOS-Technologie des Megabitsspeichers /1/ die Beherrschung minimaler Strukturmaße um 1 Mikrometer nicht nur eine technologische Herausforderung an die Verfahrensentwickler, sondern ebenso an die Ausrüstungsentwickler, die unter anderem mit den Elektronenstrahl-anlagen ZBA 21 und den optischen Strukturübertragungsanlagen AÜR des Kombinates VEB Carl Zeiss JENA entscheidende Vorleistungen erbringen mußten. Gleiches gilt für viele andere Betriebe. Hierin liegt eine der Katalysatorwirkungen der Mikroelektronik: Sie erfordert modernste Hochtechnologien in nahezu allen Bereichen der Volkswirtschaft und liefert zugleich entscheidende Voraussetzungen zur Erzielung derartiger Spitzenleistungen. Speicherschaltkreise eignen sich nun aufgrund ihrer logisch einfachen, regulären Struktur und ihrer außerordentlichen Empfindlichkeit gegenüber technologischen Schwankungen hervorragend als Testobjekte für die Entwicklung neuer Technologien und deren materiell-technischer Basis. Werden Speicherschaltkreise eines neuen technologischen Niveaus, das sich in der Regel vom Vorgängerniveau durch einen vierfach höheren Integrationsgrad und damit einhergehende Steigerung der Signalverarbeitungsgeschwindigkeit im Schaltkreis unterscheidet, mit akzeptabler Ausbeute beherrscht, kann auf dem soliden Fundament einer solchen **Basistechnologie** die Entwicklung eines breiten Sortimentes von Mikroprozessoren, Logikschaltkreisen, ASICs usw. erfolgen. In diesem Sinne war die Technologie des 256-KBit-DRAMs Basis für alle heute gebräuchlichen 32-Bit-Mikroprozessoren, während die Technologie des Megabitsspeichers zu einer neuen Klasse von Mikroprozessoren führen wird, die die Leistungsfähigkeit heutiger Superrechner erreichen, wie das Beispiel des Prozessors 80860 der Firma Intel zeigt. Mit der weiteren Integrationsgradsteigerung, die mit den Etappen 4-MBit-DRAM, 16-MBit-DRAM und 64-MBit-DRAM (130 Mio Transistoren pro Chip!) bereits konzipiert ist, wird der Weg frei zur Integration kompletter elektronischer Systeme auf einem Chip. Künftig wird es für die Konkurrenz-

Bernd Junghans studierte von 1962 bis 1968 Elektronik am Moskauer Energetischen Institut. Danach war er wissenschaftlicher Aspirant und Oberassistent an der Sektion Physik/Elektronische Bauelemente der damaligen Technischen Hochschule (heute Technische Universität) Karl-Marx-Stadt. Seit 1976 arbeitet Bernd Junghans in unterschiedlichen Funktionen im Forschungszentrum Mikroelektronik Dresden, wo er sich mit Technologie- und Schaltkreisentwicklungen beschäftigt, zuletzt als Projektleiter des Megabitsspeichers. Bernd Junghans ist Honorarprofessor an der Sektion Informatotechnik der Technischen Universität Dresden. Für seine Arbeiten wurde er zweimal mit dem Nationalpreis ausgezeichnet.

fähigkeit ganzer Industriezweige und Volkswirtschaften entscheidend sein, ob diese Technologie der Systemintegration beherrscht wird und verfügbar ist. Deshalb hat unsere Republik in den letzten Jahren große Anstrengungen unternommen, die Mikroelektroniktechnologie auf internationalem Spitzenniveau zu entwickeln. Bereeder Ausdruck für die dabei erzielten Erfolge ist die Herstellung erster 1-Megabitsspeicher zum 39. Jahrestag der DDR im Kombinat VEB Carl Zeiss JENA auf der Grundlage eigener Entwicklungsleistungen. Zum 40. Jahrestag kann bereits eine den wichtigsten Bedarf deckende Pilotproduktion dieses Schaltkreises abgerechnet werden, die eine gute Grundlage für weitere Schaltkreisentwicklungen in diesem technologischen Spitzenniveau bildet. Für die nächste Etappe, die mit dem Prototyp des 4-MBit-DRAMs ein Integrationsniveau von fast 10 Mio Transistoren pro Chip ermöglichen wird, laufen konzentrierte Arbeiten, um zum 41. Jahrestag unserer Republik die ersten funktionsfähigen Schaltkreise herstellen zu können.

Diese zielstreibige Entwicklung der Technologie der Höchstintegration ist ein entscheidender Faktor für die Zukunftssicherung unserer hochentwickelten Elektronikindustrie und darunter auch der Mikroprozessortechnik. Sie hat darüber hinaus Bedeutung für unsere gesamte Volkswirtschaft, wie E. Honecker feststellte: „Die weitere Entwicklung der DDR als modernes, leistungsfähiges Industrieland ist ohne die Mikroelektronik nicht vorstellbar.“ /2/

## Literatur

- /1/ Junghans, B.; Raab, M.: CSGT5 – eine moderne Basis-technologie für die Höchstintegration. Jenaer Rundschau 34 (1989) 1, S. 15

/2/ Honecker, E.: Aus dem Bericht des Politbüros an die 7. Tagung des ZK der SED. Dietz Verlag, Berlin 1988, S. 30

# Der Megabitsspeicher U 61000

**Dr. Jens Knobloch, Andreas Scade**

**VEB Forschungszentrum Mikroelektronik Dresden**

## Überblick

Die größten zur Zeit produzierten Halbleiter-Speicher mit wahlfreiem Zugriff (RAM = random access memory) sind dynamische Speicher. Diese RAMs werden mit der dynamischen Ein-Transistorzelle realisiert, weil alle anderen Zellkonzepte, beispielsweise statische Speicherzellen mit 4 oder 6 Transistoren, eine deutlich größere Fläche beanspruchen, was die Erzeugung gleichgroßer statischer Speicher im gleichen Technologieniveau verhindert.

Der dynamische Megabitsspeicher (1-MBit-DRAM) U 61000 ist der erste DDR-Schaltkreis – und damit Technologietreiber – auf der Basis einer n-Wannen-CMOS-Technologie im Strukturriveau bis  $1\mu\text{m}$  (CSGT5d). Dieses Strukturriveau und die Anwendung von vier Leitbahnen (2 × Polysilizium und je 1 × Molybdänsilicid und Aluminium) erlauben eine sehr hohe Packungsdichte, so daß der Chip in kleine Standardgehäuse montiert werden kann. Die Herstellungstechnologie des Megabitsspeichers ist in Tafel 1 charakterisiert. Auf der 4. Umschlagseite (oben) ist die Herstellung des Speichers in drei Bearbeitungsetappen dargestellt.

Tafel 1 Herstellungstechnologie CSGT5d

- 430 Teilschritte

- 18 fotolithografische Strukturierungen

- minimales Strukturraster:  $2,5\mu\text{m}$

- Oxiddicke der Speicherkapazität:  $12\text{ nm}$

- Zellengröße:  $3,8 \times 9,0 = 34,2\mu\text{m}^2$

- Chipfläche:  $5,1 \times 12,85 = 65,5\mu\text{m}^2$

- Integrationsgrad: 2,3 Mio Bauelemente

- Eine Skalierung des Chips ist in Vorbereitung

- effektive minimale Kanallängen:  $1\mu\text{m}$

Der U 61000 besitzt die Organisation  $1048576 \times 1$  Bit und arbeitet im *Fast Page Mode* (FPM). Er ist vorwiegend für den Einsatz in der Rechen- und Nachrichtentechnik und in der Industrielektronik vorgesehen und wird durch folgende Haupt-eigenschaften charakterisiert:

- dynamischer Schreib-/Lesespeicher mit wahlfreiem Zugriff

- hohe Arbeitsgeschwindigkeit und geringe Verlustleistung entsprechend Tafel 2

- TTL- und CMOS-Kompatibilität der Ein- und Ausgänge

- Tristate-Ausgangsstufen

- Betriebsspannung:  $5\text{ V} \pm 10\%$

- 512 Refreshzyklen; Refreshzeit: 8 ms

- Betriebsarten im Normalbetrieb und im Fast Page Mode:

READ CYCLE

EARLY WRITE CYCLE

READ MODIFY WRITE CYCLE

- Refreshmodi:

### RAS ONLY REFRESH

### CAS BEFORE RAS REFRESH

### HIDDEN REFRESH (READ und WRITE)

- Betriebstemperatur:  $0^\circ\text{C} \dots 70^\circ\text{C}$ .

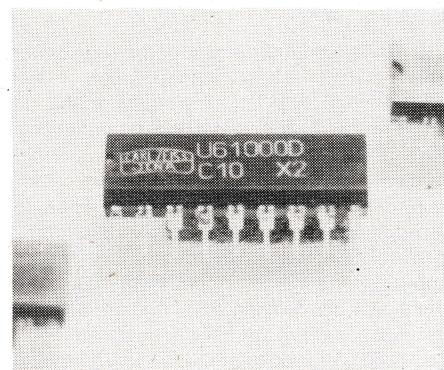

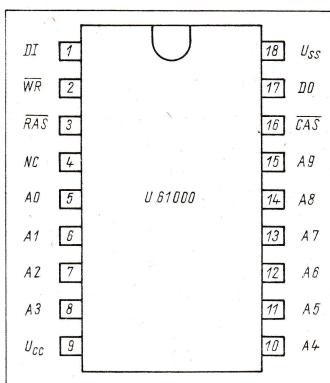

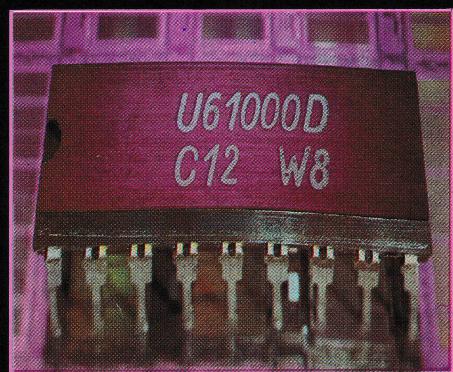

Der Schaltkreis wird in einem 18poligen DIL-Plastgehäuse mit  $7,62\text{ mm}$  Reihenabstand verkappt. Im Entwicklungszeitraum kann auch ein 18poliges Keramik-DIP-Gehäuse zum Einsatz kommen.

In diesem Fall lauten die Typenbezeichnungen U 61000 CC12 und U 61000 CC10.

Ein Gehäuse in Aufsetztechnik (SOJ 26/20) mit verringertem Platzbedarf ist in Vorbereitung.

Eine vollständige Übersicht über die Eigenschaften des Megabitsspeichers U 61000 ist in der TGL 45536 (in Vorbereitung) enthalten.

## Aufbau

Das speichernde Element der dynamischen Zelle ist ein Kondensator. Die dort gespeicherte Ladung repräsentiert die Information. Außer dem Kondensator enthält die Speicherzelle noch einen Auswahltransistor, über den die Information vom Kondensator auf die Bitleitung (Lesen) oder umgekehrt von der Bitleitung in den Kondensator (Schreiben) gelangen kann. Die Auswahl der Speicherzellen erfolgt durch ein überhöhtes Potential auf der Zeilen- oder Wortleitung.

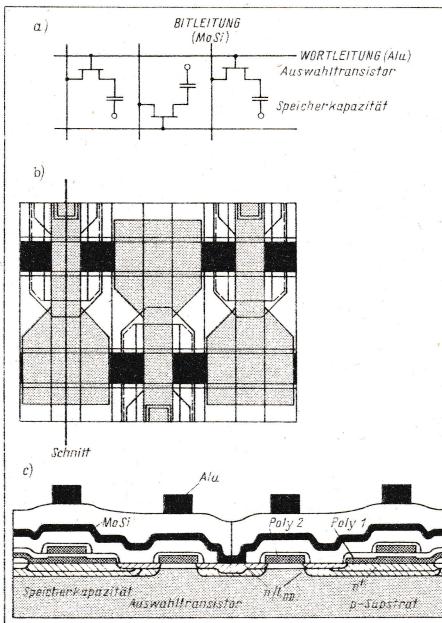

Der U 61000 arbeitet mit einer planaren Ein-Transistorzelle, deren Schaltbild, Layout und Längsschnitt in Bild 1 dargestellt sind. Für höherintegrierte Speicher (z. B. 4-MBit-DRAMs) zeichnen sich neue Lösungen der Kondensatorherstellung ab, um bei weiterer Zellverkleinerung die Speicherkapazität in

Tafel 2 Geschwindigkeits- und Leistungsparameter des U 61000

|                  | U 61000 DC12<br>Grundtyp | U 61000 DC10<br>Selektionstyp |

|------------------|--------------------------|-------------------------------|

| RAS-Zugriffszeit | 120 ns                   | 100 ns                        |

| CAS-Zugriffszeit | 45 ns                    | 35 ns                         |

| FPM-Zugriffszeit | 60 ns                    | 50 ns                         |

| Zykluszeit       | 220 ns                   | 190 ns                        |

| FPM-Zykluszeit   | 70 ns                    | 55 ns                         |

| Betriebsstrom    | max. 50 mA               | max. 60 mA                    |

| Ruhestrom        |                          |                               |

| bei CMOS-Pegel   | max. 1 mA                | max. 2 mA                     |

| bei TTL-Pegel    |                          |                               |

Bild 1 Speicherzelle U 61000

a) Schaltung b) Layout c) Längsschnitt

Jens Knobloch (45) studierte Regelungstechnik und war anschließend als wissenschaftlicher Assistent an der Technischen Universität Dresden tätig. 1974 promovierte er zum Thema „Entwurf bipolarer Assoziativspeicher“.

Seit 1973 arbeitet er auf dem Gebiet des Entwurfs integrierter Schaltkreise im heutigen Forschungszentrum Mikroelektronik Dresden. Hier war er maßgeblich an der Entwicklung integrierter MOS-Speicher und deren Entwurfsgrundlagen beteiligt.

1988 verteidigte er die Promotion B „Entwurf und Entwurfsstechnologie integrierter Schaltkreise“. Jens Knobloch ist Themenleiter für die Entwicklung des 1-MBit-DRAMs. Für seine Arbeiten wurde er zweimal mit dem Nationalpreis ausgezeichnet.

Andreas Scade (31) studierte von 1978 bis 1983 an der Technischen Universität Karl-Marx-Stadt und diplomierte über organische Halbleiter.

Seit 1983 arbeitet er im Forschungszentrum Mikroelektronik Dresden als Spezialist für dynamische Speicher. Er war Themenleiter Schaltungsoptimierung für die Ausbeuteentwicklung des 64-KBit-DRAMs.

Bei der Entwicklung des 1-MBit-DRAMs ist er verantwortlicher Entwickler der Gesamt-Schaltungskonzeption und Themenleiter für die Entwicklung des verbreiterten Typspektrums des Megabitsspeichers.

der notwendigen Größenordnung von zirka  $40\text{ fF}$  zu erhalten. Da die Information als Ladung in einem Kondensator gespeichert wird, geht sie durch Leckströme mit der Zeit verloren. Man muß daher in sogenannten Refresh-Zyklen die Ladung regenerieren.

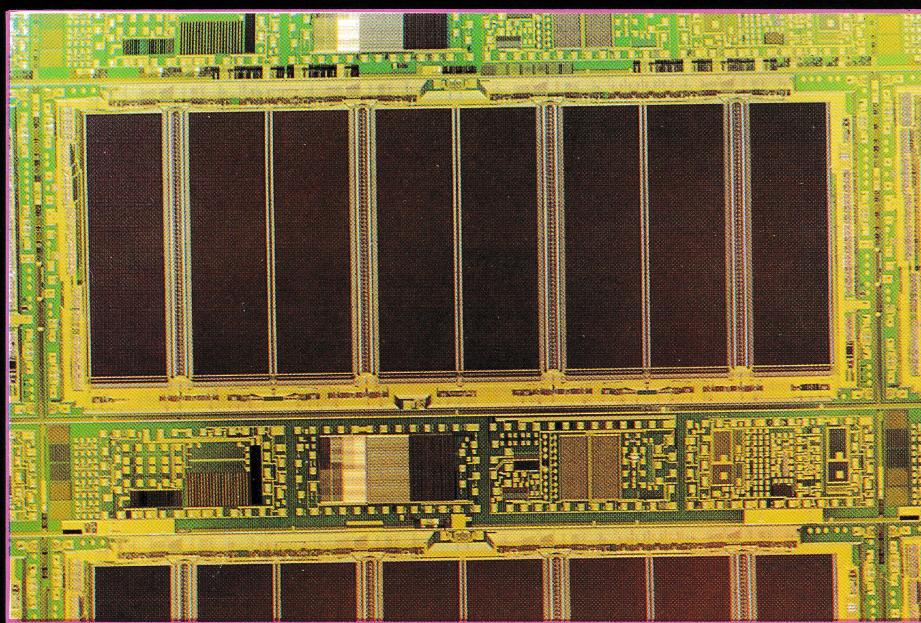

Die Speicherzellen sind auf dem Chip in Form einer Matrix angeordnet. Diese Speichermatrix wird in der Regel in Teilmatrizen zerlegt, deren Größe und Anordnung eine Optimierung der technologischen Größen Widerstand und Kapazität der Leitungen und der elektrischen Parameter Verzögerungszeit und Signalerkennung darstellt. Durch den Einsatz des Aluminiums kann die Wortleitung des 1-MBit-DRAMs zugunsten einer kurzen Bitleitung mit kleiner Kapazität und damit einer besseren Signalerkennung relativ lang ausgeführt werden. Die Matrixstruktur wird außerdem durch die Zielstellung einer internen 4-Bit-Organisation bestimmt, die aus Gründen der Leistungseinsparung, der Anwendung eines 4fach-Testmodus und des Einsatzes des gleichen Chips für einen Speicher mit der Organisation  $256\text{ K} \times 4$  gewählt wurde. Das Foto auf der 4. Umschlagseite links unten zeigt die resultierende Matrixstruktur beim U 61000.

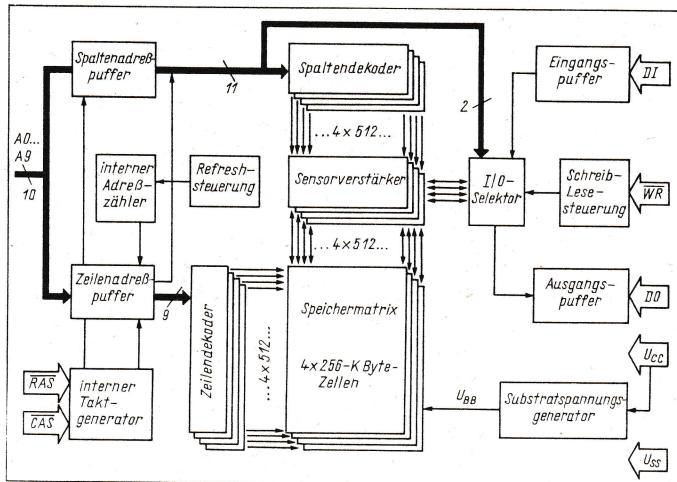

Die Ansteuerung der Matrix, die Taktbläufe und die Datenein- und Datenausgaben werden von den peripheren Schaltungen realisiert, die die Matrix umgeben. Das entsprechende Blockschaltbild ist in Bild 2 dargestellt. Über Bondinseln (siehe 4. Umschlagseite oben) und Schaltkreispins wird die Verbindung des Chips zur Leiterplatte hergestellt. Bild 3 zeigt die Anschlußbelegung des U 61000. Bedingt durch die Hinzunahme eines weiteren Adreßanschlusses A9 konnte das bis zum 256-KBit-DRAM übliche 16polige Gehäuse nicht beibehalten werden. Durch das 18polige Gehäuse bleibt ein freies Pin 4 übrig, welches nicht angeschlossen ist oder für einen besonderen Testmodus genutzt werden kann.

## Bild 2 Blockschaltbild 1-MBit-DRAM U 61000

**Bild 3 Anschlußbelegung des U 61000**

|         |                |                 |                     |

|---------|----------------|-----------------|---------------------|

| A0...A9 | Adresseingänge | RAS             | Zeilenadreßstrobe   |

| WR      | Schreib-/      | CAS             | Spaltenadreßstrobe  |

|         | Lesesteuerung  | U <sub>cc</sub> | Betriebsspannung    |

| DI      | Dateneingang   | U <sub>ss</sub> | Masse               |

| DO      | Datenausgang   | NC              | nicht angeschlossen |

Mit der durch das Zeilenadreßbit A9 festgelegten Hälfte (1024 Bit) des Sensorregisters kann praktisch wie mit einem statischen Speicher gearbeitet werden, was im Fast Page Mode ausgenutzt wird.

Im Refreshzyklus (Auffrischungszyklus) entfällt die Manipulation an den einzelnen Bits, da hier durch internes Lesen, Verstärken und Rückschreiben jeweils zweier Zeilen nur die durch Leckströme veränderte Ladung der Speicher kondensatoren wiederhergestellt wird. Darum muß in diesem Fall keine Spaltenadresse bereitgestellt werden.

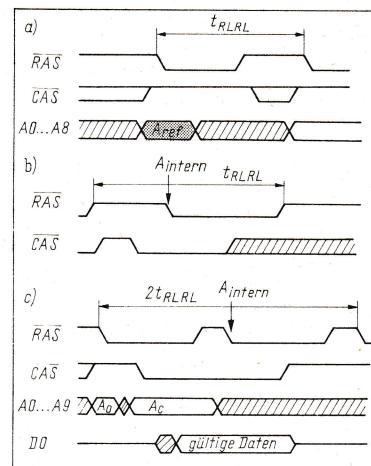

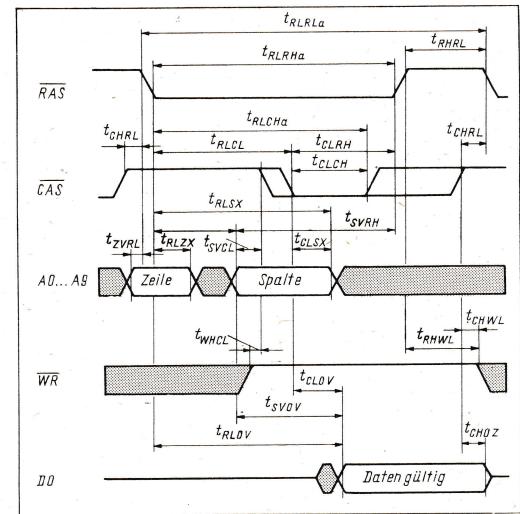

## Auffrischen

Alle Zeilen des Megabitsspeichers müssen innerhalb von 8 ms einmal aktiviert oder aufgefrischt werden, damit die Information in den Speicher kondensatoren auch unter ungünstigen Bedingungen (Grenzen von Betriebsspannung und Temperatur, fertigungsbedingte Toleranzen der Leckströme einzelner Zellen usw.) nicht verlorengeht. Dazu stehen drei Techniken zur Verfügung (Bild 4):

- RAS only refresh

- Hidden refresh

- CAS before RAS refresh.

Der **RAS-only-Refresh** ist die Standardform der Refreshsteuerung. Der Zyklus beginnt (wie jeder andere Speicherzyklus auch) mit einer aktiven RAS-Flanke (High-Low), zu der die passende Zeilenadresse an den Adreßeingängen bereitstehen muß. Der CAS-Eingang sollte inaktiv (High) bleiben, wodurch der Ausgang seinen hochohmigen Zustand behält und eine geringere Leistung verbraucht wird. Da nur 512 Refreshadressen erforderlich sind, wird das Adreßsignal A9 ignoriert.

Im Inneren vollzieht sich der schon beschriebene Ablauf des Auslesens, Verstärkens und Rückschreibens in der Zeile mit der angelegten Adresse. Dieser Vorgang muß innerhalb der Refreshzeit von 8 ms in jeder der 512 verschiedenen Refreshadressen mindestens einmal erfolgen, damit die Information nicht verlorengeht. Dies kann sowohl in gleichmäßigen Zeitabständen erfolgen, zum Beispiel durch Auffrischen jeweils einer Zeile nach

zirka 15  $\mu$ s, als auch im Burst-Betrieb, das heißt Auffrischen aller Zeilen unmittelbar hintereinander mit einer anschließenden längeren Phase ohne Refresh. Wenn sichergestellt ist, daß innerhalb der genannten Zeit in jeder Zeile mindestens ein normaler Speicherzugriff stattfindet, kann man auf einen zusätzlichen Refreshvorgang ganz verzichten. Der Zeitbedarf für das Auffrischen beträgt weniger als 1,5 % des normalen Speicherbetriebes.

Beim **Hidden-Refresh** und beim **CAS-before-RAS-Refresh** wird die benötigte Refreshadresse von einem chipinternen Adreßzähler bereitgestellt. Damit entfällt der Aufwand für deren externe Bereitstellung, und die Adreßeingänge können während dieser Refresharbeiten beliebige Werte annehmen. Das Inkrementieren des internen Adreßzählers erfolgt nach jedem Zugriff.

Beim Hidden-Refresh kann man einen Refresh-Zyklus nach einem vorhergehenden Lesezyklus (oder Schreibzyklus) durchführen. Dazu bleibt das CAS-Signal am Speicher ununterbrochen aktiviert und damit die gelesene Information am Ausgang weiterhin gültig, während im Schaltkreis der Refresh abläuft. Das RAS-Signal muß dabei nach einem ordnungsgemäßen Lesezugriff zunächst inaktiviert und anschließend erneut aktiviert werden. Der Hidden-Refresh läuft also im Hintergrund in einem zusätzlichen Speicherzyklus ab.

Beim CAS-before-RAS-Refresh wird der interne Refreshvorgang durch eine geeignete Kombination der Signale RAS und CAS ausgelöst. Ist das CAS-Signal bei der RAS-Vorderflanke aktiv (Low), wird die im internen Adreßzähler vorgegebene Zeile aufgefrischt.

Zum Testen der ordnungsgemäßen Funktion des Adreßzählers kann im *Counter test cycle* mit der internen Refreshadresse – von außen ergänzt um die fehlenden Zeilenadresse – auf die Daten zugegriffen werden. Dieser Test muß mit acht CAS-befor-RAS-Zyklen zur Initialisierung des Adreßzählers eingeleitet werden. Anschließend werden zuerst bei festgehaltener Spaltenadresse in 512 Zyklen Daten in jede Zeile geschrieben. Diese Daten werden anschließend bei gleicher Spaltenadresse in 512 Zyklen wieder ausgelesen und getestet. Durch Wiederholen dieses Tests mit komplementären Daten wird die richtige Funktion des Adreßzählers gesichert.

## Speicherzugriffe

Der Zugriff auf eine bestimmte Adresse erfor-

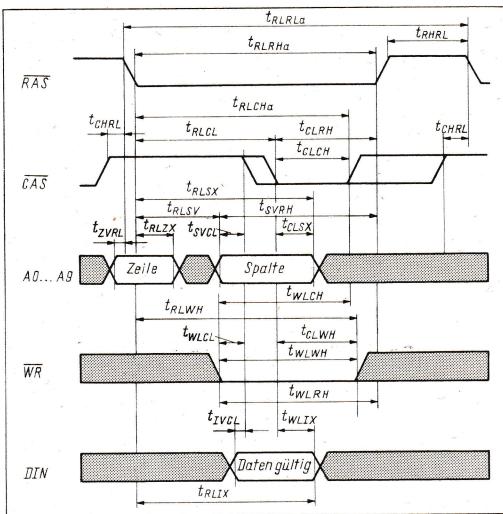

**Bild 5 EARLY WRITE CYCLE**

(graue Flächen: Pegel nicht defi-

niert)

### Bild 6 READ CYCLE (graue Flächen: Pegel nicht defi- niert)

dert im Gegensatz zum Refresh die Übertragung von beiden Adreßhälften, also Zeilen- und Spaltenadresse, die bei der aktiven Flanke (High-Low) des jeweiligen Strobe-Signals RAS oder CAS gültig sein müssen. Dabei entscheidet der Pegel des Lese-Schreibsteuerungssignals WR während der CAS-Low-Flanke, ob es sich um einen Lese- oder einen Schreibzyklus handeln soll. Neben diesen beiden wichtigsten Betriebsarten gibt es bei den verschiedenen Typen der 1-MBit-DRAMs eine Reihe von typspezifischen Varianten, die eine andere Zugriffsorganisation mit höherer Arbeitsgeschwindigkeit beinhalten. Neben dem im U 61000 gewählten *Fast Page Mode* können das der *Static Column Mode* oder der *Nibble Mode* sein. Alle im folgenden Abschnitt genannten Zeiten beziehen sich auf den U 61000 DC12.

## Schreibzyklus

Bild 5 zeigt das Zeitdiagramm eines Schreibzugriffs. Das Schreibsignal WR ist während der aktiven CAS-Flanke auf Low-Potential, und etwa zur gleichen Zeit muß die Information am Dateneingang D1 gültig sein. Nach Ablauf der aktiven Low-Phase von RAS und CAS können diese Signale wieder inaktiv werden. Bevor der nächste Zyklus gestartet werden kann, braucht der Speicher etwas Zeit für interne Umladevorgänge (precharge time), weswegen die Zykluszeit bei dynamischen Speichern größer ist als die Zugriffszeit. Da bei diesem sogenannten Early-Write-Zyklus der Datenausgang DO hochohmig bleibt und im nachfolgend beschriebenen Lesezyklus die Information am Dateneingang D1 beliebig sein kann, lassen sich beide Anschlüsse miteinander verbinden (Common I/O). Dies kann beim Anschluß des Speichers an den Datenbus eines Mikroprozessorsystems genutzt werden: Allerdings sind dann nicht mehr alle Sonderbetriebsarten des Speicherschaltkreises möglich.

## Lesezyklus

Im Gegensatz zum Schreibzyklus muß beim Lesezyklus (Bild 6) das Schreibsignal während der gesamten CAS-Low-Phase inaktiv bleiben. Von besonderem Interesse beim Lesezyklus sind die Zugriffszeiten. Wegen der zwei Strobe-Signale muß man zwischen den Zugriffszeiten von RAS und CAS unterscheiden. Außerdem wirkt unter bestimmten Bedingungen auch die Adressezugriffszeit. Diese Bedingungen werden durch den Abstand der aktiven Flanken von RAS und CAS

und durch den Vorhalt der Spaltenadresse vor der aktiven CAS-Flanke bestimmt. Je nach Wahl dieser Zeiten wird die Zugriffszeit von RAS, von CAS oder vom Adreßwechsel bestimmt.

Mit den spezifischen Werten des U 61000 DC12

$$\begin{array}{ll}

t_{RLOVmax} = 120 \text{ ns} & t_{RLCLmin} = 25 \text{ ns} \\

t_{CLOVmax} = 45 \text{ ns} & t_{SVCLmin} = 0 \text{ ns} \\

t_{SVOVmax} = 60 \text{ ns} & t_{RLSVmin} = 20 \text{ ns}

\end{array}$$

ergeben sich die in Bild 7 dargestellten Zu-

griffszeiten.

Mit dem Übergang von CAS in den inaktiven Zustand (High) gehen die Ausgänge wieder in den hochohmigen Zustand zurück, während RAS inaktiv werden kann, ohne daß die Ausgänge des Speichers ungültig werden (Hidden refresh). Die Zykluszeit im Schreib- und im Lesezyklus beträgt 220 ns. Geringere Zyklus- und Zugriffszeiten werden mit dem Fast Page Mode erreicht.

## Read-Modify-Write-Zyklus

Die Grundidee eines Read-Modify-Write-Zyklus ist: In *einem* Zugriff auf eine Speicherzelle diese erst lesen und dann beschreiben. Wenn dabei der neue Speicherinhalt vom alten Inhalt abhängt, daß heißt, wenn die Schreibinformation aus den gelesenen Daten erzeugt wird, liegt ein echter Read-Modify-Write-Zyklus vor. Wie die Schreibdaten erzeugt werden, ist vom Speicher völlig unabhängig. Wird WR sofort nach Ablauf der Zugriffszeit aktiv, so wird eine Verarbeitung der gelesenen Daten nicht abgewartet, und

The diagram illustrates the timing sequence for a 3D DRAM access. The vertical axis represents time, with labels for  $t_{SVCL}/ns$  and  $t_{RCLC}/ns$ . The horizontal axis represents the number of cycles, with labels for 50 and 100. The sequence of events is as follows:

- RAS:** A pulse starting at cycle 0.

- CAS:** A pulse starting at cycle 10, labeled  $t_{RLSV}$  and  $t_{SVCL}$ .

- AS:** A pulse starting at cycle 20.

The time interval between the end of the RAS pulse and the start of the CAS pulse is  $t_{RCLC}$ . The time interval between the end of the CAS pulse and the start of the AS pulse is  $t_{SVCL}$ . The time interval between the end of the AS pulse and the end of the RAS pulse is  $t_{CLOV}$ .

Two shaded regions are shown:

- A triangular region between the RAS and CAS pulses, labeled  $t_{RLSV}$ .

- A trapezoidal region between the CAS and AS pulses, labeled  $t_{SVOV}$ .

A constraint is shown:  $t_{RCLC} \geq t_{SVCL} + t_{RLSV\ min}$ .

Bild 7 Wirksame Zugriffszeiten des U 61000 DC12 in Abhängigkeit von der RAS-CAS-Verzögerungszeit  $t_{RLCL}$  und der Spaltenadreßvorhaltzeit  $t_{SVCL}$

die bereits an DI anliegenden Daten werden geschrieben. In diesem Fall spricht man von einem Read-Write-Zyklus, der sich im grund- sätzlichen Ablauf vom Read-Modify-Write- Zyklus nicht unterscheidet.

Der zeitliche Ablauf eines Read-Modify-Write-Zyklus beginnt als normaler Lesezugriff, jedoch wird nach Ablauf der Zugriffszeiten das Schreibsignal WR aktiviert. Die dabei am Speichereingang DI liegende Information gelangt dadurch in die adressierte Zelle. Es ist klar, daß in einem echten Read-Modify-Write-Zyklus erst nach dem Lesen und einer Modifizierung der gelesenen Daten geschrieben werden kann.

Die Zykluszeit eines Read-Write-Zyklus beträgt 255 ns. Beim schon beschriebenen Early-Write-Zyklus bleibt der Speicheraus-

**Bild 8 FAST PAGE MODE READ CYCLE**

(graue Flächen: Pegel nicht definiert)

gang hochohmig. Kommt die aktive Flanke von WR jedoch nach der aktiven CAS-Flanke, aber vor Ablauf der Zugriffszeit, kann weder von einem Early-Write- noch von einem Read-Write-Zyklus sicher gesprochen werden, weil der Ausgang kurzzeitig unbestimmt ist und damit keine gültigen Lesedaten garantiert sind. Da jedoch das einwandfreie Schreiben gesichert ist, wird diese Betriebsart auch Late-Write-Zyklus genannt.

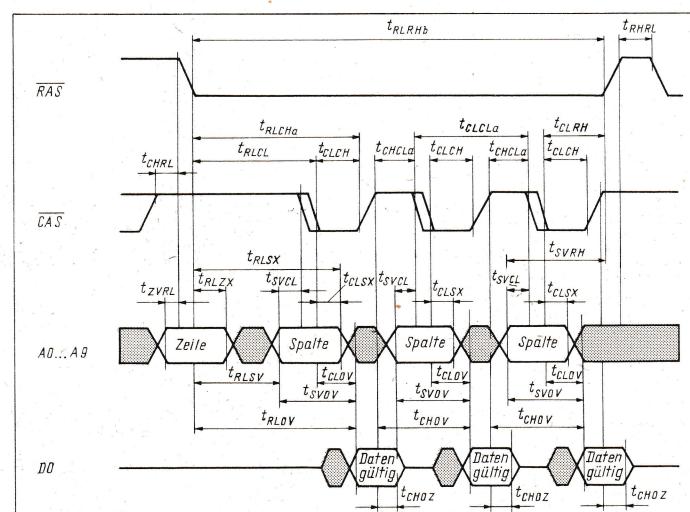

### Fast Page Mode

Der **Fast Page Mode** erlaubt eine höhere Datenrate als der Normalbetrieb. Bei dieser Betriebsart erfolgen die Zugriffe in einem bestimmten Bereich des Speichers, nämlich einer Seite (page) von 1024 Bit. Es handelt sich dabei um eine Zeile der Speichermatrix, die durch die Zeilenadresse definiert ist. Der Vorteil des Fast Page Mode liegt darin, daß bei aufeinanderfolgenden Zugriffen innerhalb einer Seite die Zeilenadresse nur zu Beginn einmal übertragen werden muß und für jeden weiteren Zugriff lediglich die Spaltenadresse erforderlich ist. Bild 8 zeigt die Lesezyklen im Fast Page Mode. Schreibzyklen und Read-Modify-Write-Zyklen laufen entsprechend ab. Der Fast Page Mode wird dadurch ausgelöst, daß mit RAS auf Low die Zeilenadresse gehalten wird, während mit jeder aktiven CAS-Flanke unter der angelegten Spaltenadresse ein Zyklus abläuft. Bei Lesezyklen gelten ähnliche Zusammenhänge bezüglich Zugriffszeit, wie im Abschnitt Lesezyklus beschrieben.

Im Fast Page Mode ist die dynamische Verlustleistung geringer, weil der interne Zugriff auf die ganze Zeile der Matrix nur zu Beginn erforderlich ist, während jeder weitere Zugriff nur noch eins der vorselektierten Bits betrifft. Zu beachten ist allerdings, daß eine Seite nicht beliebig lange aktiviert sein kann. Zum einen ist aufgrund interner dynamischer Vorgänge (floating Wortleitung kann nicht beliebig lange überhöhtes Potential führen) die RAS-Pulsbreite auf 100  $\mu$ s begrenzt, zum anderen sei an den regelmäßig erforderlichen Refresh erinnert.

Im Unterschied zum Fast Page Mode wird im **Static Column Mode** ein Speicherzyklus innerhalb der „Seite“ durch den Spaltenadreßwechsel ausgelöst, ohne daß eine aktive CAS-Flanke erforderlich ist. Damit arbeitet der Speicher in dieser Betriebsart wie ein vollstatischer, ungetakteter Speicher. Aufgrund der nicht mehr erforderlichen Synchronisation mit CAS und dem damit verbundenen Wegfall einer CAS-Vorladezeit verringert sich die Zykluszeit beim Static Column Mode.

Wegen der großen Ähnlichkeit von Static Column Mode und Fast Page Mode ist es möglich, beim U 61000-Chip durch Änderung einer Maskenebene beide Betriebsarten von einem Grundentwurf abzuleiten.

### Verlustleistung

Ein nicht unwesentlicher Aspekt bei der Auswahl von Speicherschaltkreisen ist deren Verlustleistung. Dies ist nicht im Sinne des Energiesparens zu verstehen, sondern weil durch geringe Leistungsaufnahme des Speichersystems der Aufwand bei der Spannungsversorgung (Netzteile) sinkt und eine netzunabhängige Versorgung, zum Beispiel mit Notlaufbatterien vereinfacht oder überhaupt erst möglich wird.

Die Verlustleistung von dynamischen Speichern wird im wesentlichen von drei Anteilen im Stromverbrauch, dem Ruhestrom, dem Betriebsstrom und dem Refresh-Strom, bestimmt.

Der **Ruhestrom**, der aufgrund der verwendeten CMOS-Technik sehr niedrig liegt, ist immer aufzubringen und dient dem Ausgleich von internen Leckströmen und dem Erzeugen interner Referenzspannungen. Durch Anlegen von CMOS-Pegeln, besonders an RAS und CAS, kann die Ruhestromaufnahme deutlich gegenüber der Verwendung von TTL-Pegeln gesenkt werden, was in zwei verschiedenen Werten für den Ruhestrom spezifiziert ist. ( $I_{CCR1} = 2 \text{ mA}$ ,  $I_{CCR2} = 1 \text{ mA}$ )

Der **Betriebsstrom** wird hauptsächlich durch die Stromimpulse bei internen Umladevorgängen hervorgerufen, die immer dann auftreten, wenn Pegeländerungen an den Strobe-Eingängen RAS und CAS auftreten. Die spezifizierte Stromaufnahme ( $I_{CC0} = 50 \text{ mA}$ ) gilt für die minimale Zykluszeit und sinkt bei langsamerem Betrieb des Speichers im Verhältnis von minimaler zu tatsächlicher Zykluszeit. Liegen die Strobe-Signale längere Zeit auf Low-Potential, spricht man auch von einer aktiven statischen Stromaufnahme, die aber stets kleiner als die dynamische Stromaufnahme ist. Im Falle des Fast Page Mode ist eine geringere Betriebsstromaufnahme spezifiziert ( $I_{CC2} = 30 \text{ mA}$ ), da nur noch die durch CAS ausgelösten Umladevorgänge ablaufen, die die Matrix mit ihren großen Kapazitäten nicht berühren.

Der **Refresh-Strom** ist etwas geringer als der Betriebsstrom, da die Ausgangstreiber und weitere periphere Schaltungen beim Auffrischen nicht aktiviert werden. Der spezifizierte Wert ( $I_{CC1} = 50 \text{ mA}$ ) unterscheidet sich allerdings nicht von  $I_{CC0}$ . Innerhalb der Refreshzeit  $t_{Ref} = 8 \text{ ms}$  sind 512 Refreshzyklen erforderlich, womit der Mittelwert dieses Stromanteils folgendermaßen ermittelt wird:

$$I_{CCRef} = I_{CC1} \times \frac{t_{RLRL}}{t_{Ref}} \times 512$$

Zusätzlich zu diesen drei Stromanteilen ist der Ausgangsstrom an DO prinzipiell zu berücksichtigen. Meist kann er allerdings vernachlässigt werden, weil  $I_{CC0}$  oft wesentlich größer als der Ausgangsstrom ist.

Die Verlustleistung ergibt sich aus der Summe dieser Stromanteile, multipliziert mit der maximalen Versorgungsspannung, wobei es sinnvoll ist, diesen Wert für eine konkrete Speicherkonfiguration (Leiterplatte o. ä.) zu berechnen. Damit ergibt sich:

$$P_{Vmax} = (I_{CC0} \times j + I_{CC1} \times k + I_{CCRef} \times i) \times U_{CCmax}$$

$i$  = Gesamtzahl der Speicherschaltkreise

$j$  = Anzahl der aktiven Schaltkreise

$k = i - j$  = Anzahl der inaktiven Schaltkreise

Im folgenden Beispiel soll die Verlustleistung einer Speicherkonfiguration berechnet werden. Eine Speicherplatine mit einer Organisation von 4 M  $\times$  16 Bit soll bei minimaler Zykluszeit betrieben werden. Damit ergibt sich:

$$i = 64 \text{ Schaltkreise U 61000}$$

$$j = 16 \text{ Schaltkreise U 61000}$$

$$k = 48 \text{ Schaltkreise U 61000}$$

Mit den spezifizierten Werten des U 61000 DC12:

$$I_{CC0} = 50 \text{ mA (Normalbetrieb)}$$

$$I_{CCR1} = 2 \text{ mA (Ansteuerung mit TTL-Pegeln)}$$

$$I_{CC1} = 50 \text{ mA}$$

$$t_{RLRL} = 220 \text{ ns}$$

$$t_{Ref} = 8 \text{ ms}$$

erhalten wir drei Stromanteile

$$I_{CC0} \times j = 800 \text{ mA}$$

$$I_{CC1} \times k = 96 \text{ mA}$$

$$I_{CCRef} \times i = \frac{50 \times 512 \times 220 \times 64}{8 \times 10^6} = 45 \text{ mA}$$

Als maximale Gesamtverlustleistung für die gewählte Speicherkonfiguration ergibt sich damit:

$$P_{Vmax} = (800 + 96 + 45) \times 5,5 \text{ mW} = 5,18 \text{ W}$$

### Betriebsbedingungen

#### Betriebsspannung, Temperatur

Die Betriebsspannung für 1-MBit-DRAMs liegt generell bei  $U_{CC} = 5 \text{ V} \pm 10\%$  im Temperaturbereich von 0 bis 70 Grad Celsius. Jedoch ist kein Speicher so dimensioniert, daß diese Werte nur knapp eingehalten werden, weil dann Fertigungstoleranzen sofort zu fehlerhaften Bauelementen führen würden. Zielstellung ist es, daß die Schaltkreise bis zu Betriebsspannungsabweichungen von über 20 % arbeiten. Hauptproblem des Speichers sind hohe Temperaturen, da die Selbstentladung der Speicher kondensatoren exponentiell mit der Temperatur ansteigt, was zu einer Unterschreitung der spezifizierten Refreshzeit und einem damit verbundenen Datenverlust führt. Neben der Verlustleistung des Speichersystems sind auch die Flankensteilheiten und Spitzenwerte der Stromimpulse bei der Auslegung der Spannungsversorgung wichtig. Um zu verhindern, daß die Betriebsspannung bei Stromspitzen zu stark zusammenbricht, sind schaltkreisinterne Maßnahmen durch entsprechende Stütz kondensatoren auf der Leiterplatte zu ergänzen.

In diesem Zusammenhang sei noch das Verhalten beim Anlegen der Versorgungsspannung erwähnt. Eine interne Logik sorgt für ein gezieltes, stufenweises Zuschalten der Funktionsgruppen des Speichers. Damit wird ein *Latch-up* beim Einschalten wirkungsvoll verhindert, wenn ein ordnungsgemäßer Betriebsspannungsanstieg von kleiner als 0,1 V je ns gewährleistet ist. Eine weitere Forderung beim Einschalten ist, nach dem Erreichen von  $U_{CC} 200 \mu\text{s}$  zu warten und anschließend 8 RAS-Zyklen zu durchlaufen. Mit dieser *wake-up-procedure* wird gesichert, daß alle internen Pegel auf dem richtigen Wert liegen und der Speicher voll funktionsfähig ist.

### Ein- und Ausgangspegel

Die Ein- und Ausgänge des U 61000 sind TTL-kompatibel. CMOS-Schaltkreise lassen sich leichter ansteuern als TTL-Schaltkreise, da ihre Pegel in der Nähe der Betriebsspannungspotentiale  $U_{CC}$  und  $U_{SS}$  liegen. Neben der höheren Störsicherheit ist damit auch eine geringere Ruheverlustleistung verbunden.

Flankensteilheiten der Steuersignale von 5 ns und geringer sichern die spezifizierte Arbeitgeschwindigkeit. Damit ist allerdings ein Überschwingen der Eingangssignale verbunden. DRAM-spezifisch ist ein negatives Überschwingen von  $-1 \text{ V}$  und ein positives Überschwingen auf  $6,5 \text{ V}$  zulässig. In diesem Zusammenhang sei auch noch erwähnt, daß es in schnellen oder auch räumlich ausgedehnten Speichersystemen zu störenden Reflexionen auf den Daten- und den Taktleitungen kommen kann.

### Soft-Errors

Ein wichtiges Problem bei dynamischen Speichern sind die sogenannten Soft-Errors. Diese sind einmalige Fehler, die durch Ein-

wirkung von Alphateilchen auf den Speicher kondensator, die Bitleitung oder den Leseverstärker verursacht werden. Diese Teilchen entstehen beim radioaktiven Zerfall von Uran, Thorium und weiteren Elementen, die in Spuren in jedem Gehäusematerial vorkommen.

Beim Durchgang von Alphateilchen durch die genannten Gebiete werden Ladungsträgerpaare erzeugt, und die im p-Substrat als Minoritätsladungsträger entstehende Elektronenwolke kann in die n-leitenden Speicher-

gebiete gelangen und die gespeicherte Information vernichten. Abgesehen von der falschen Information wird der Speicher dabei nicht beschädigt. Gemessen werden die Soft-Errors in der Einheit *fit*, die angibt, wieviel Fehler in  $10^9$  Betriebsstunden auftreten.

Durch die Verwendung strahlungssarmer Gehäusematerialien und durch Implantation einer Potentialbarriere unterhalb der Speicher kondensatoren und Bitleitungen, die eine Elektronenwolke unwirksam macht, ist beim

U 61000 eine geringe Soft-Error-Empfindlichkeit erreicht worden.

## KONTAKT

VEB Forschungszentrum Mikroelektronik Dresden, PSF 34, Grenzstraße 28, Dresden, 8080; Tel. 58 8420

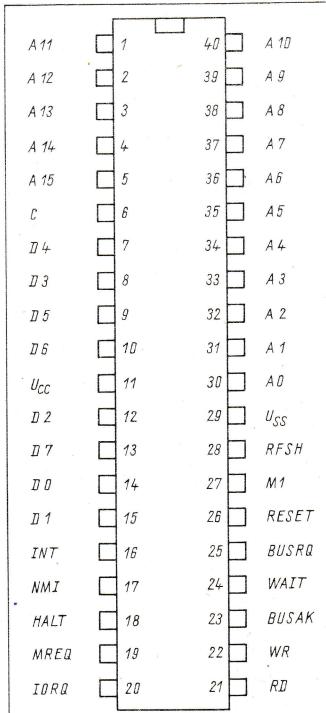

# 8-Bit-CMOS-Mikroprozessorsystem U 84C00

**Michael Ritter**

VEB Mikroelektronik „Karl-Marx“

Erfurt, Forschungszentrum

## Vorbemerkungen

Eine Betrachtung des internationalen 8-Bit-Mikroprozessor-Marktes zeigt den Trend, daß in den letzten Jahren eine große Anzahl von Systemen in CMOS-Technologie eingeführt wurde. Dabei wurden einige grundsätzliche Gemeinsamkeiten deutlich. Erstens werden immer ganze Familien, das heißt Prozessoren und zugehörige Peripherieschaltkreise, in der neuen Technologie gefertigt. Zweitens versuchen alle Hersteller, CMOS-Prozessoren anzubieten, die kompatibel zu bestehenden NMOS-Lösungen sind. Drittens ist eine erkennbare Gemeinsamkeit, daß Weiterentwicklungen der klassischen 8-Bit-Prozessoren mit verbesserten Architekturen angeboten werden. So entstanden zum Beispiel der 80C85 (Intel) aus dem 8080 und der HD64180 (Hitachi) aus dem Z80. Vom international dominierenden 8-Bit-Prozessorsystem Z 80 existieren diverse Weiterentwicklungen in CMOS-Technologie. Unter anderem bieten Zilog, Toshiba, Sharp und Hitachi solche Systeme an.

Im VEB Mikroelektronik „Karl-Marx“ Erfurt (MME) wird die Familie U 84C00 in CMOS-Technologie als Weiterentwicklung der Familie U 880 gefertigt. Diese Schaltkreise eignen sich vor allem zum Einsatz in mobilen Meßgeräten und Handheld-Computern. Sie können aber auch in bestehenden Lösungen die Schaltkreisfamilie U 880 ablösen.

## Die Schaltkreisfamilie U 84C00

### Vorstellung

Die Schaltkreisfamilie U 84C00 ist ein leistungsfähiges 8-Bit-Mikroprozessorsystem in CMOS-Technologie, welches neben der CPU eine Reihe von Peripheriebauteilen umfaßt. Die Schaltkreise werden in den Frequenzklassen 2,5 MHz und 4,0 MHz angeboten. Zu einigen Typen gibt es Anfallbauteile mit der Bezeichnung U 84Cxx DC02-1. Diese unterscheiden sich von den Standardtypen dadurch, daß sie nicht in den Schlafzustand übergehen können. Alle anderen Parameter entsprechen denen der Standardbauteile. Tafel 1 zeigt eine Übersicht über die vom MME angebotenen Typen.

## Vergleich der Familien U 84C00 und U 880

Die Schaltkreise der Familie U 84C00 sind grundsätzlich kompatibel zu den Schaltkreisen der Familie U 880. Das gilt für alle Befehle ebenso wie für alle Hardwareparameter einschließlich der TTL-Inkompatibilität des Takteinganges (siehe auch Bilder 1 und 2). Da die Schaltkreisfamilie in CMOS-Technologie gefertigt wird, besitzt sie gegenüber Schaltkreisen der U 880-Familie den gewichtigen Vorteil des geringen Stromverbrauchs. Für den Anwender sind damit Applikationslösungen möglich, die sich durch geringe Eigenwärmung, kleinere Netzteile und kleinere Gehäuse auszeichnen. Außerdem ist der Einsatz von Batterien zur Stromversorgung mit vertretbarem Aufwand möglich. Tafel 2 zeigt einen Vergleich der Stromaufnahme der Schaltkreise der U 84C00-Familie mit der der U 880-Familie.

Ein CMOS-Bauelement besteht aus Grundbausteinen, die aus komplementären Feldefekttransistoren aufgebaut sind. Im statischen Betrieb ist immer nur einer der beiden Transistoren leitend. Die Verlustleistung wird im wesentlichen durch Leckströme bestimmt. Während eines Umschaltvorganges müssen die Gatekapazitäten umgeladen werden, und beide Transistoren sind kurzzeitig leitend. Daraus folgt, daß die Verlustleistung von

Michael Ritter – Jahrgang 1961 – studierte von 1982 bis 1987 an der Technischen Hochschule Ilmenau in der Fachrichtung Informationstechnik und theoretische Elektrotechnik. Seit 1987 ist er als Applikationsingenieur in der Abteilung Mikroprozessorapplikation im Forschungszentrum des VEB Mikroelektronik „Karl Marx“ Erfurt tätig.

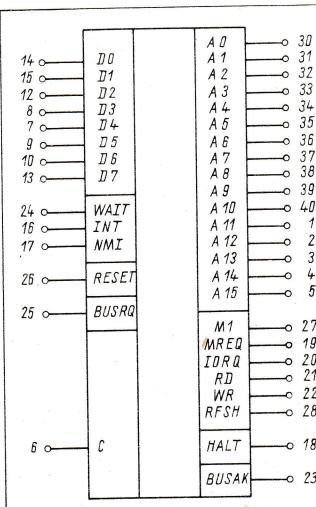

Bild 1 Pinbelegung des U 84C00

Tafel 1 Übersicht über die vom MME angebotenen Typen

| Typ  | 2,5 MHz      |                | 4,0 MHz      |

|------|--------------|----------------|--------------|

|      | Standardtyp  | Anfalltyp      |              |

| CPU  | U 84C00 DC02 | U 84C00 DC02-1 | U 84C00 DC04 |

| PIO  | U 84C20 DC02 | U 84C20 DC02-1 | U 84C20 DC04 |

| CTC  | U 84C30 DC02 | U 84C30 DC02-1 | U 84C30 DC04 |

| SIO  | U 84C40 DC02 | –              | U 84C40 DC04 |

| DART | U 84C70 DC02 | U 84C70 DC02-1 | U 84C70 DC04 |

| CGC  | U 84C97 DC02 | –              | U 84C97 DC04 |

CPU – zentrale Verarbeitungseinheit

PIO – parallele Ein-/Auszabeinheit

CTC – Zähler-/Zeitgebereinheit

SIO – serielle Ein-/Auszabeinheit

DART – asynchrone serielle Ein-/Auszabeinheit

CGC – Taktgenerator/-controller

Tafel 2 Vergleich der Stromaufnahme (4 MHz)

| Typ | U 84C00-Familie | U 880-Familie |

|-----|-----------------|---------------|

| CPU | 25 mA           | 200 mA        |

| PIO | 5 mA            | 100 mA        |

| SIO | 15 mA           | 130 mA        |

| CTC | 7 mA            | 120 mA        |

| CGC | 4 mA            | –             |

Bild 2 Schaltbild des U 84C00

## Der Megabitspeicher U 61000

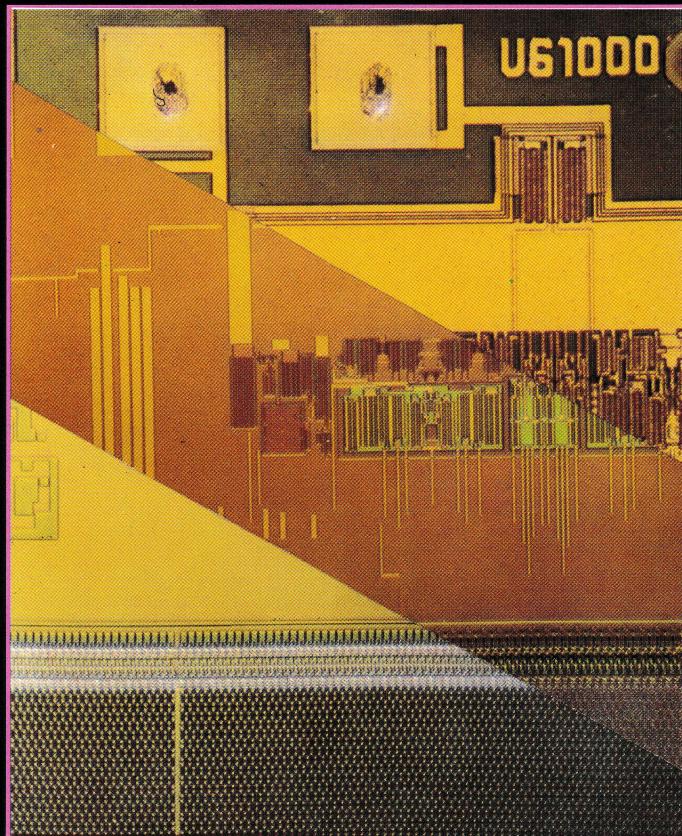

Das nebenstehende Bild zeigt einen Ausschnitt des Megabitspeichers U 61000 in den drei Bearbeitungsstufen (von unten nach oben):

- \* nach der Strukturierung der Poly-Silizium-Speicherplatte

- \* nach der Strukturierung des Molybdänsilicids

- \* nach Fertigstellung und Zwischenprüfung.

Auf dem Bild sind Teile der Speichermatrix und der Taktsteuerung sowie Bondinseln mit Testereindrücken zu erkennen.

Lesen Sie hierzu unseren Beitrag „Der Megabitspeicher U 61000“ in diesem Heft.

Layout des Megabitspeichers U 61000 und des Testfeldstreifens für Technologieentwicklung und -kontrolle. Im Bild sind deutlich die vier Teilmatrizen der internen 256-K × 4-Organisation zu erkennen. Die gut leitende Alu-Wortleitung und die höherohmige Molybdänsilicid-Bitleitung führen zur langgestreckten Form der Teilmatrizen.

18poliges Duroplastgehäuse des U 61000 in Dual-in-line-Bauform (DIL)